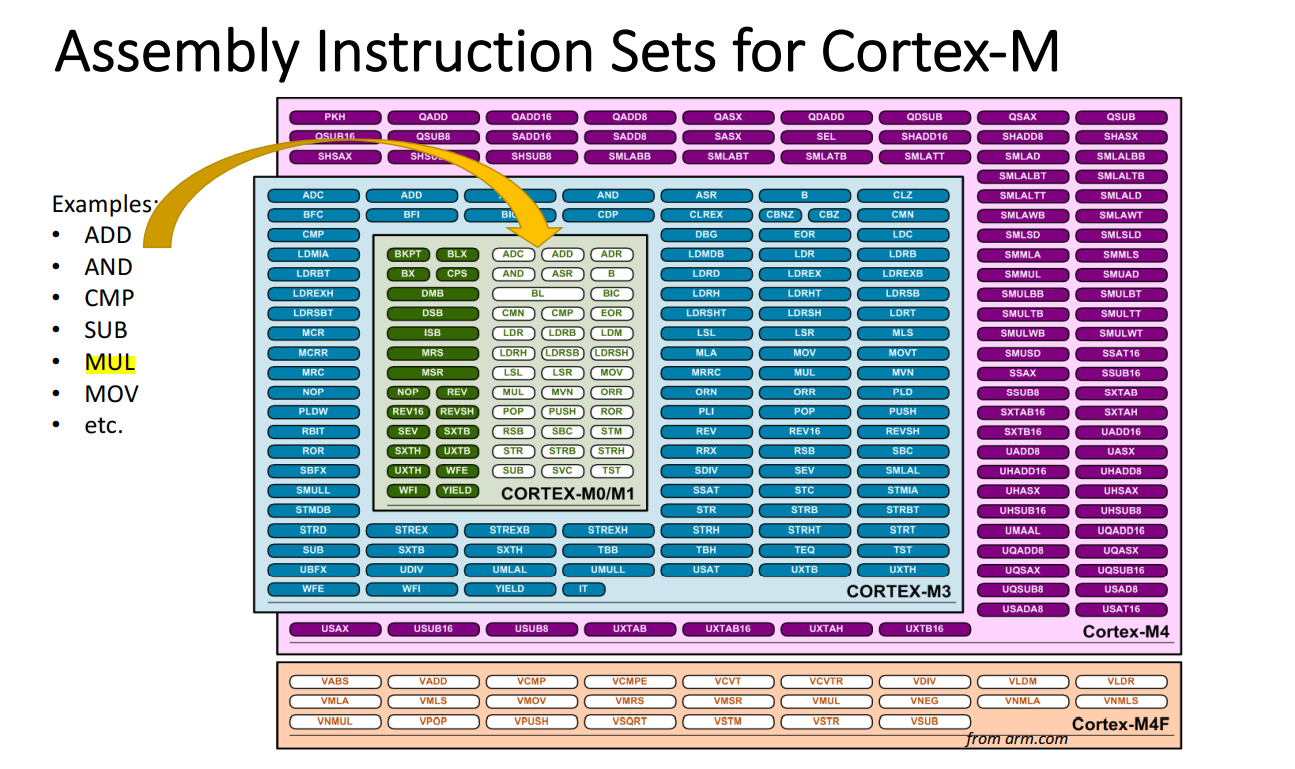

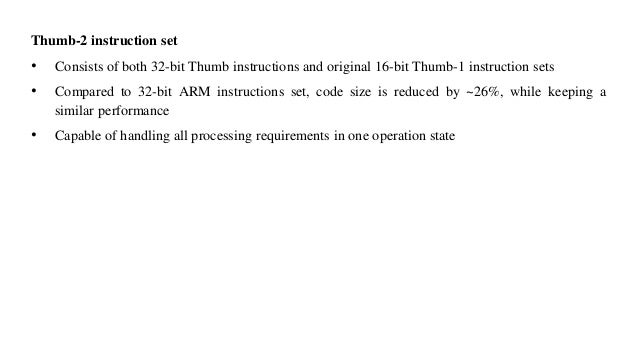

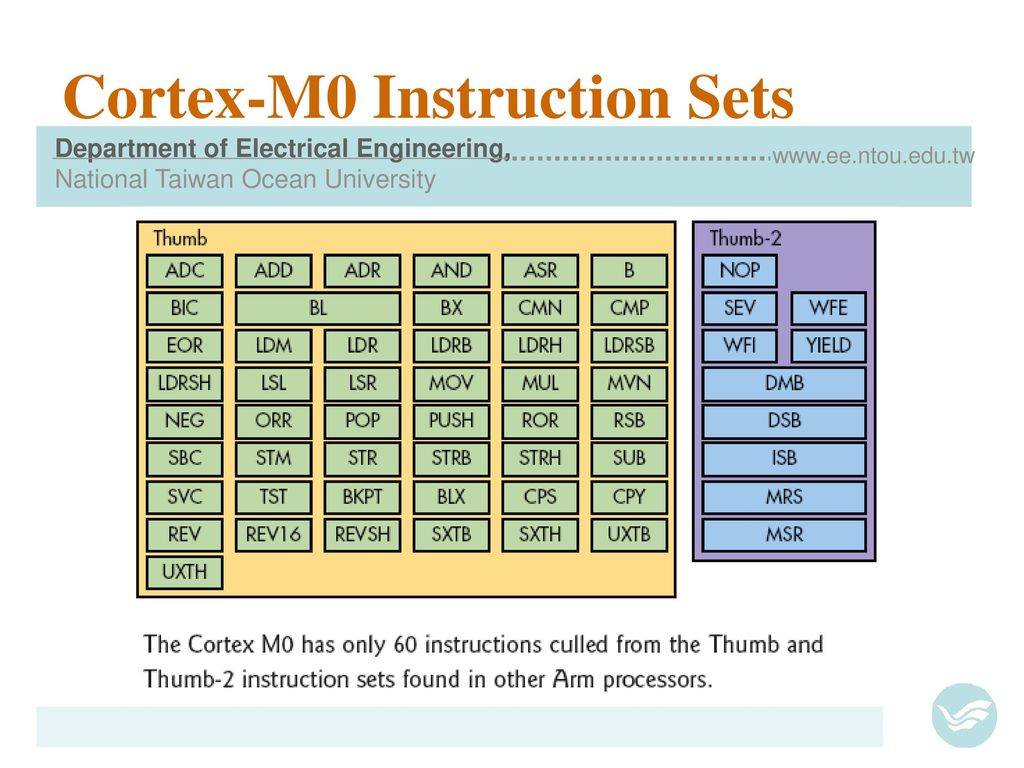

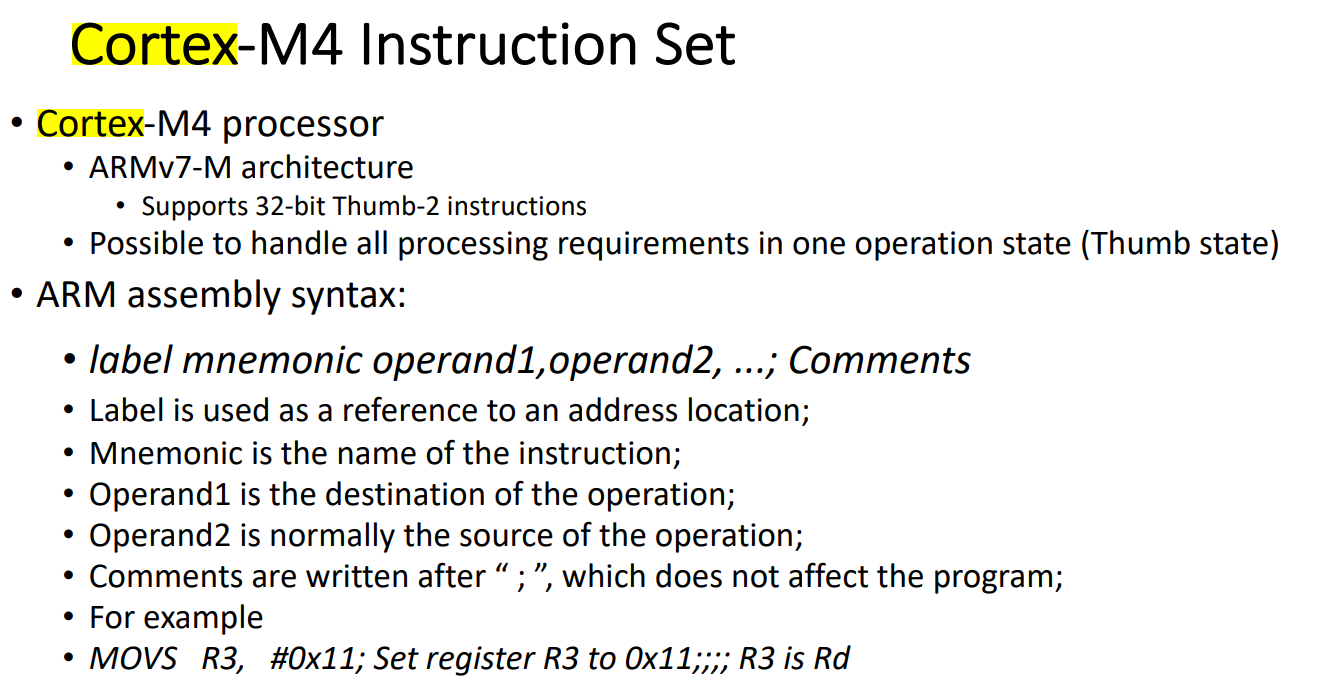

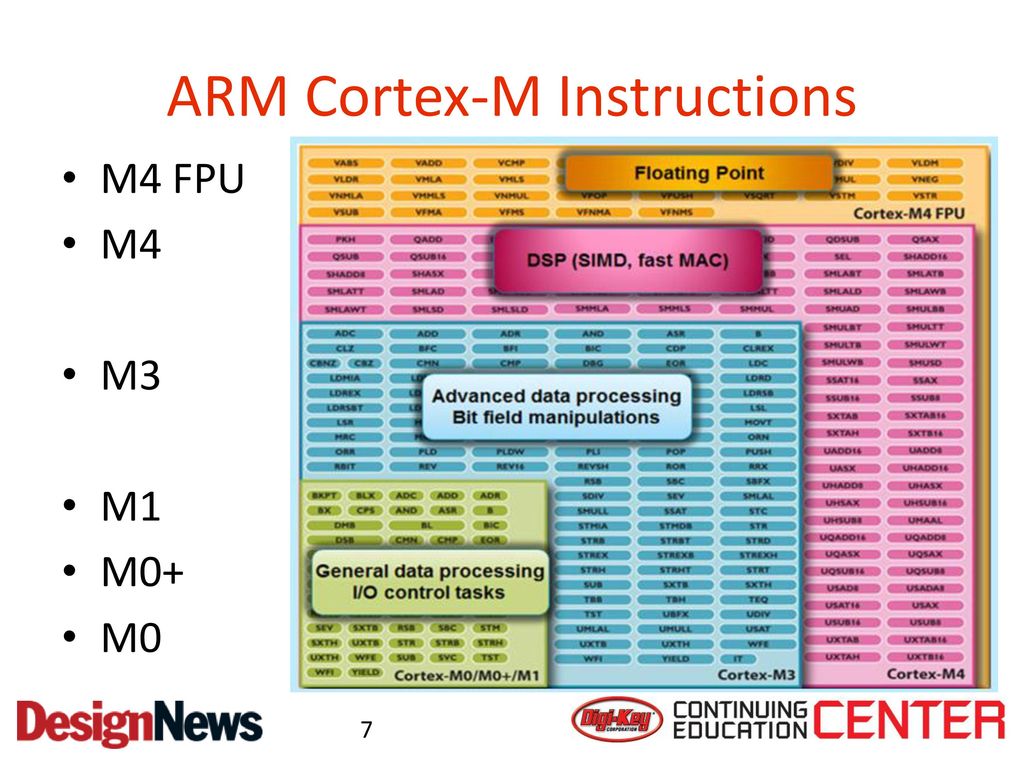

Page 192 The CortexM4 Instruction Set VMOV ARM Core register to scalar Transfers one word to a floatingpoint register from an ARM core register Syntax VMOV{cond}{32} Ddx, Rt where Is an optional condition code, see Conditional execution on page 318 cond Is an optional data size specifierThe CortexM0 is an optimized superset of the CortexM0 The CortexM0 has complete instruction set compatibility with the CortexM0 thus allowing the use of the same compiler and debug tools The CortexM0 pipeline was reduced from 3• All ARMv7 chips support the Thumb2 (& ARM) instruction set – but CortexM3 supports only the 16bit/32bit Thumb2 instruction set Universität Dortmund 16bit Thumb2 • reduce the number of bits used to identify the register – less number of registers can be used

Stm32f3xxx And Stm32f4xxx Cortex M4 Programming Manual

Cortex m4f instruction set

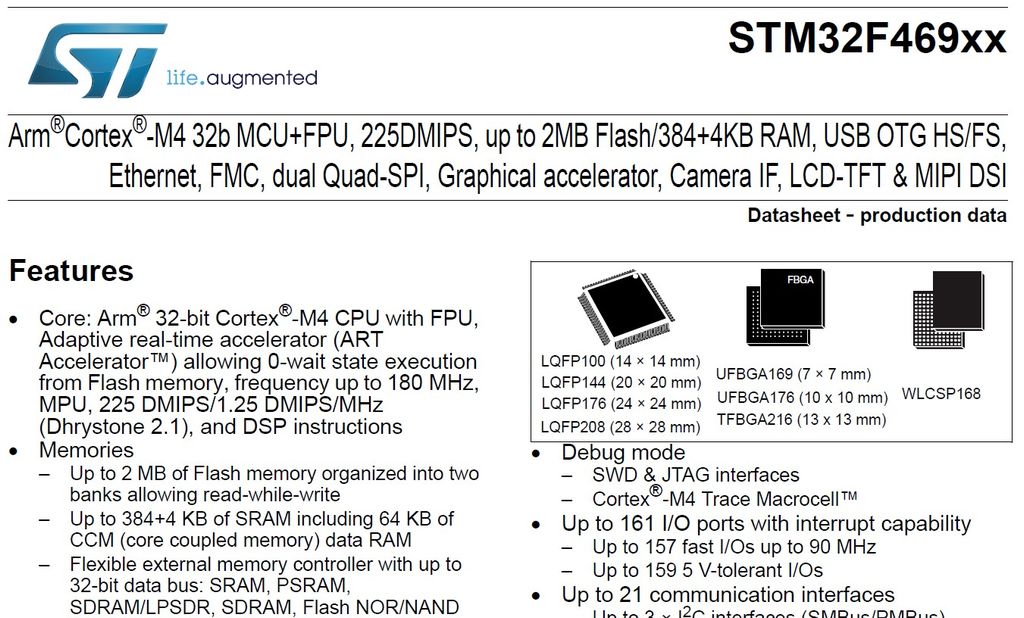

Cortex m4f instruction set-Dec 08, 17 · ARM Cortex M0 – Besides the limited logic gates and efficiency, it is designed for energyoptimized embedded applications which also require many configurations The instruction set is compatible with ARM Cortex M0, therefore the same compilator and debug tools can be used;ST's STM32F4 series features ARM Cortex M4based highperformance 32bit microcontrollers, with DSP and FPU instructions, reaching 225 DMIPS and

Arm Introduces Cortex M4 Core For Digital Signal Controllers Berkeley Design Technology Inc

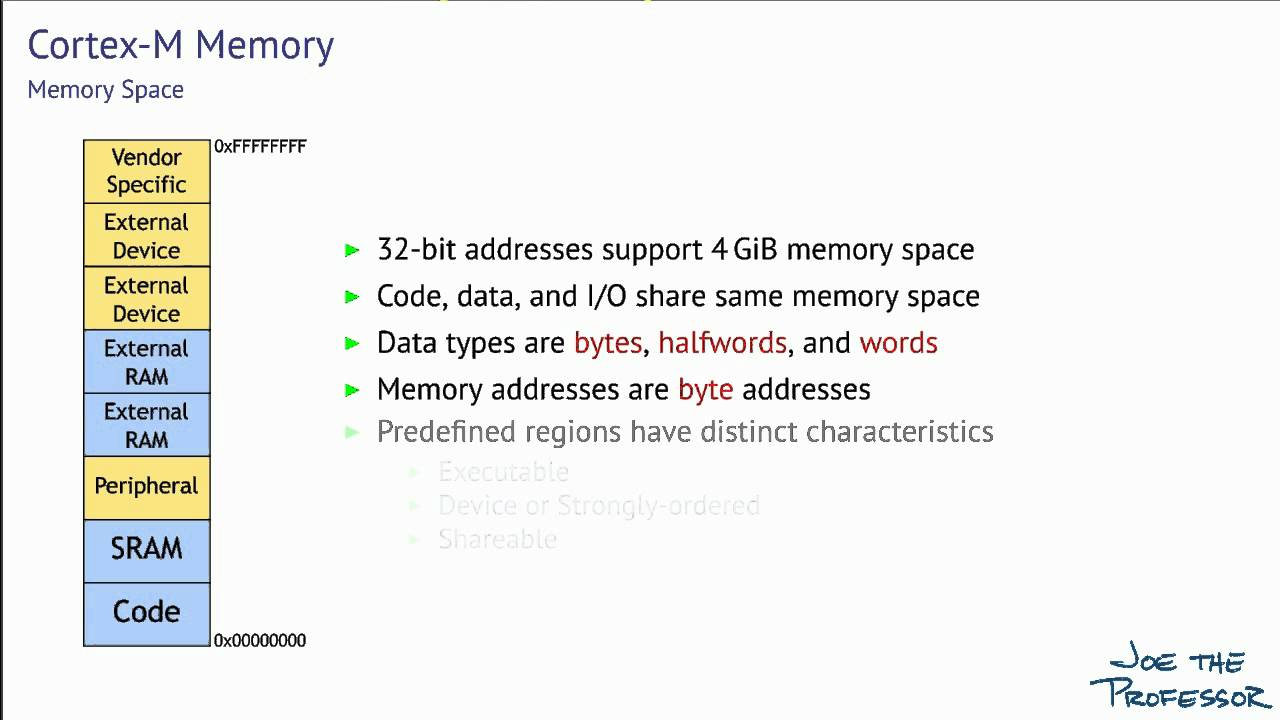

1 Introduction EachofthefollowingchaptersdescribesafunctionalgroupofCortexM3instructionsTogether theydescribealltheinstructionssupportedbytheCortexM3processorFeb 05, 18 · Instructions and data are stored in the same memory VonNeumann Harvard Data and instructions are stored into separate memories • Faster • More energy efficient • Different bus sizes • Simple and inexpensive • Access to data or instruction, one at a timeThe CortexM0 is an optimized superset of the CortexM0 The CortexM0 has complete instruction set compatibility with the CortexM0 thus allowing the use of the same compiler and debug tools The CortexM0 pipeline was reduced from 3

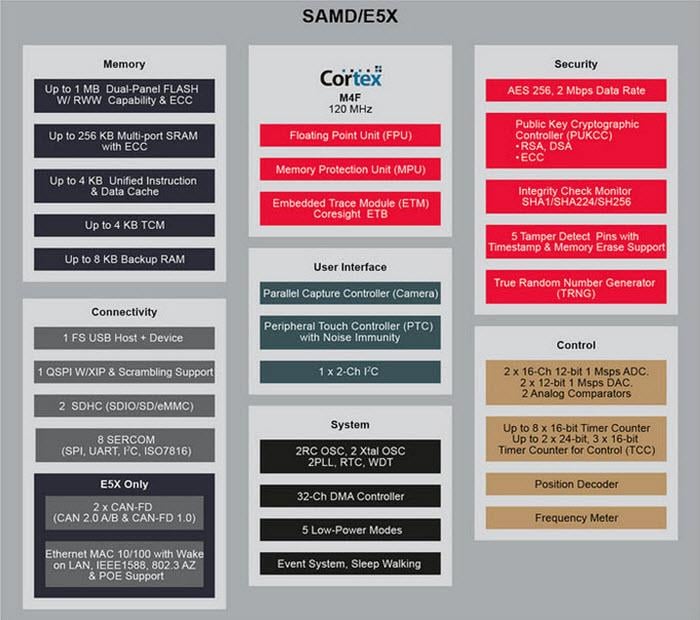

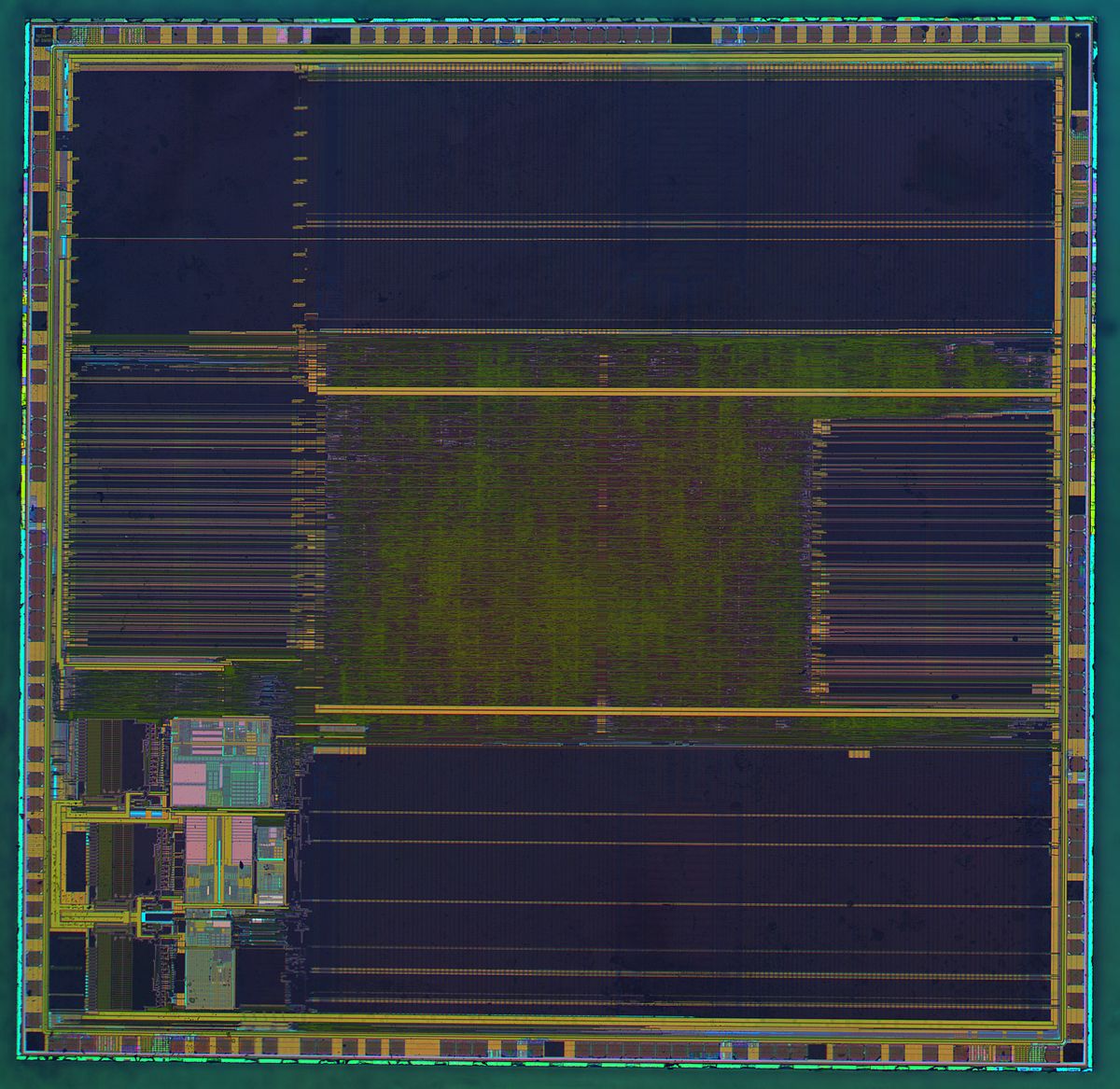

Up to 192 MHz Arm® Cortex ®M4F delivering 125 DMIPS per MHz DSP instruction set Memory Protection Unit ( MPU ) • Memory 512/ 256/ 128 KB zerowait state Flash memory 160/ 128/ 64 KB SRAM 4 KB Secure Protection ROM 2 KB OneTimeProgrammable ROM • Cyclic Redundancy Calculation Unit • 16ch Peripheral DMA Controller •Jun 07, 21 · CortexM4 hardware implementation Although the CortexM4 seems to be a simple 32bit core, it supports sophisticated mechanisms, such as exception preemption, internal bus matrix and debug units Through a tutorial, the CortexM4 low level programming is explained, particularly the ARM linker parameterizing and some tricky assembly instructionsCore ARM® 32bit Cortex®M4F CPU with FPU − 240 MHz maximum frequency, with a memory protection unit (MPU) − Singlecycle multiplication and hardware division − Floating point unit (FPU) − DSP instructions Memories − 256 to 1024 KBytes of Flash instruction/data memory − sLib configurable part of main Flash set as

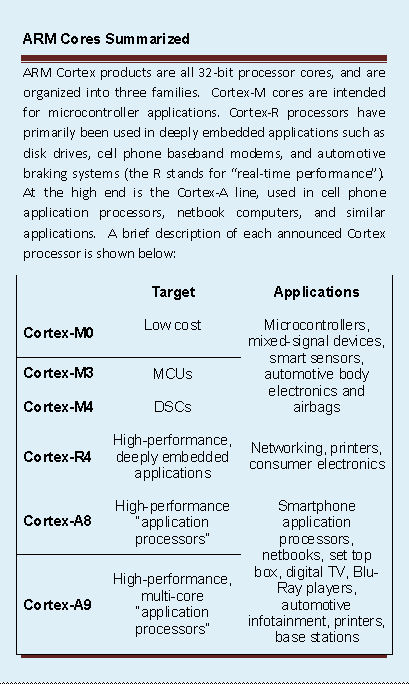

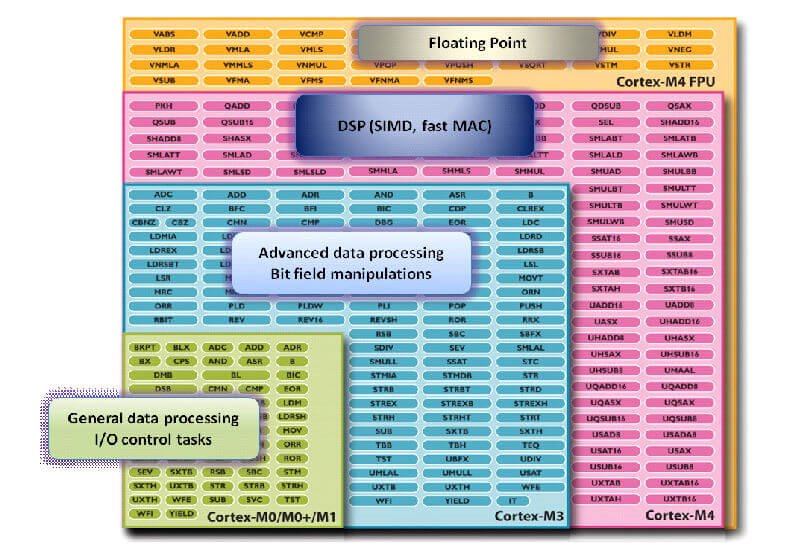

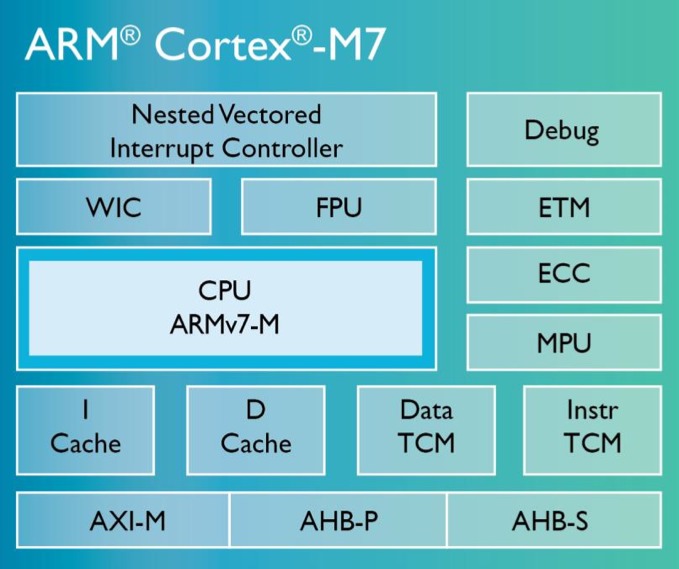

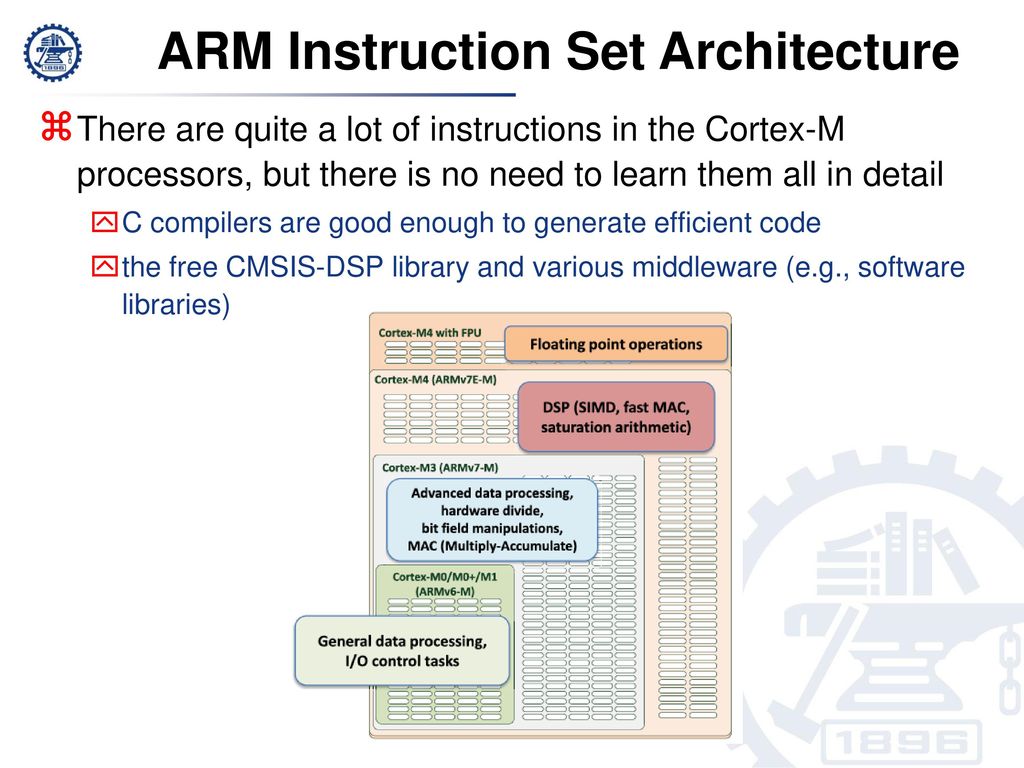

DSP for CortexM Arm's Digital Signal Controllers, the CortexM4, CortexM7, CortexM33, CortexM35P, and CortexM55 processors, address the need for highperformance generic code processing, as well as digital signal processing applications The addition of DSP extensions to the Thumb instruction set and the optional floatingpoint unit• ARM Cortex M0 core running up to 48 MHz at 125 °C • Single cycle 32 x 32 bits multiply • 2stage pipeline for further reduced power consumption • Serial Wire Debug (SWD) • Binary compatible instruction set with the ARM Cortex M4F DMA • 16 channel, extended up to 64 channel with DMA MUXIEEE 754 Compliant, Single precision FloatingPoint Unit (FPU) DSP Instruction;

Engr478 Lecture2 Intro To Tm4c123g And Arm Cortex M4 Engr 478 Engr 478 Design With Microprocessors Lecture 2 Introduction To Tm4c123 And Arm Course Hero

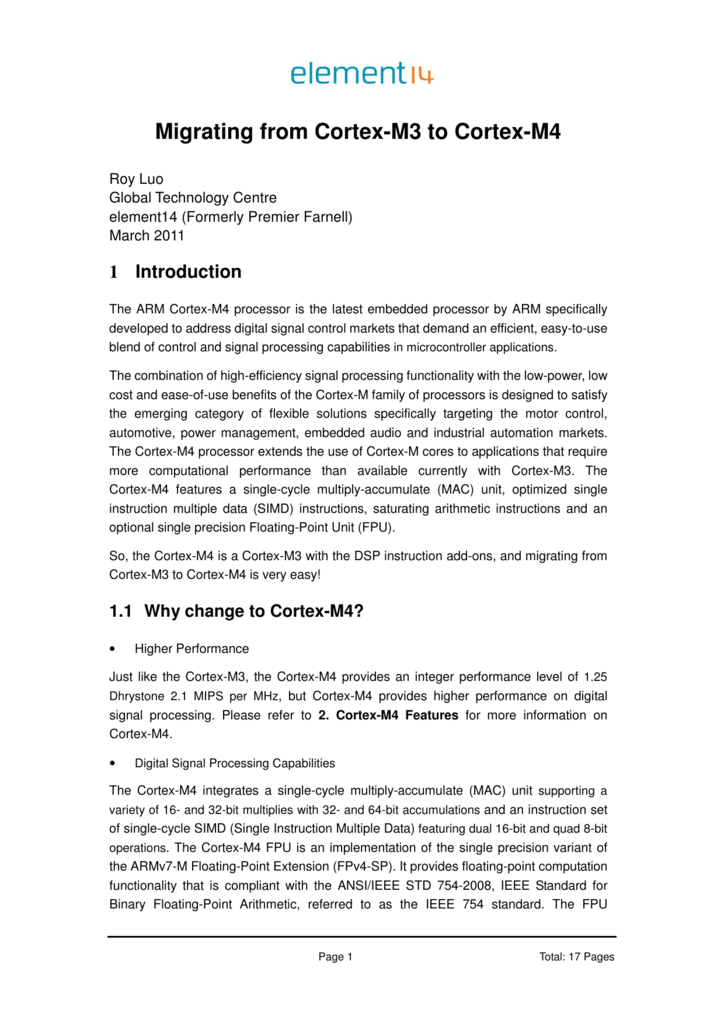

Cortexfamily

CortexM feature set comparison ARM7TDMI CortexM0 CortexM3 CortexM4 Architecture Version v4T V6M v7M v7ME Instruction set architecture ARM, Thumb Thumb, Thumb2 System Instruction Thumb Thumb2 Thumb Thumb2, DSP, SIMD, FP DMIPS/MHz 072 (Thumb), 095 (ARM) 09 125 125 Bus interfaces None 1 3 3 Integrated NVIC No Yes Yes YesDOCUMENTATION MENU DEVELOPER DOCUMENTATION Back to searchARM CortexM4 running at up to 1MHz;

Click To Edit Master Title Style Basics Of Embedded Systems Iax0230 Arm Cortex M Architecture Prof Dr Kalle Tammemae Prof Dr Ing Thomas Hollstein Ppt Download

Cortex M4 Arm Developer

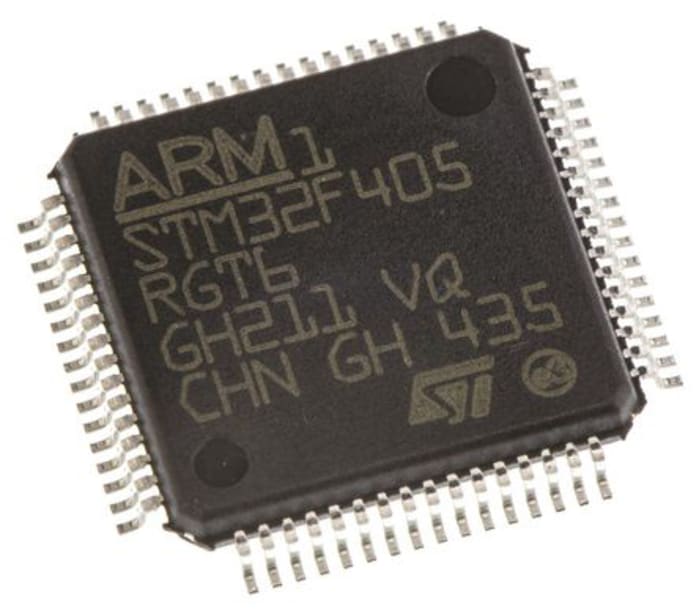

̶ ARM CortexM4F running at up to 1 MHz(1) ̶ IEEE® 754 Compliant, Singleprecision FloatingPoint Unit (FPU) ̶ DSP Instruction ̶ Thumb2 instruction set ̶ Instruction and Data Cache Controller with 2 Kbytes of Cache Memory ̶ Memories Up to 32 Kbytes of Embedded SRAM (SRAM1) for Program Code (ICode bus) and Program DataThe STM32F405xx and STM32F407xx family is based on the highperformance ARM Cortex M4 32bit RISC core operating at a frequency of up to 168 MHz The CortexM4 core features a Floating point unit (FPU) single precision which supports all ARM singleprecision dataprocessing instructions and data typesAT32F413 Series Datasheet 310 1 Ver 105 wwwarterytekcom ARM®based 32bit Cortex®M4F MCUFPU with 64 to 256 KB Flash, sLib, USB, 2 CANs, 12 timers, 2 ADCs, 13 communication interfaces Feature Core ARM® 32bit Cortex®M4F CPU with FPU − 0 all mappable on 16 external interrupt vectors MHz maximum frequency, with a

Cortexfamily

Arm Cortex M Family Introduction

That of the CortexM3 and CortexM4 at 095 DMIPS/MHz but is still compatible with its bigger brothers The CortexM0 uses a subset of the Thumb2 instruction set, and those instructions are predominantly 16bit operands (although all data operations are 32bit), which lend themselves nicely to the 2stage pipeline that the CortexM0 offersCortexM3/M4F Instruction Set Technical User's Manual (Rev A) Nov 23, 11 More literature Stellaris FuryClass Product Change Notice Jan 26, 11 White paper Serial Wire Debug—Ideal for Microcontrollers Sep 09, 10 More literature Stellaris Product Change Notice (PCN), Sept 09 Sep 07, 09 Application note512Kbytes of flash, 128Kbytes of SRAM, 8Kbytes of ROM;

How To Port From The Ark7tdmi To The Corporum3 Processor Pdf Free Download

Sam D5 E5 32 Bit Arm Cortex M4f Mcus Microchip Technology Mouser

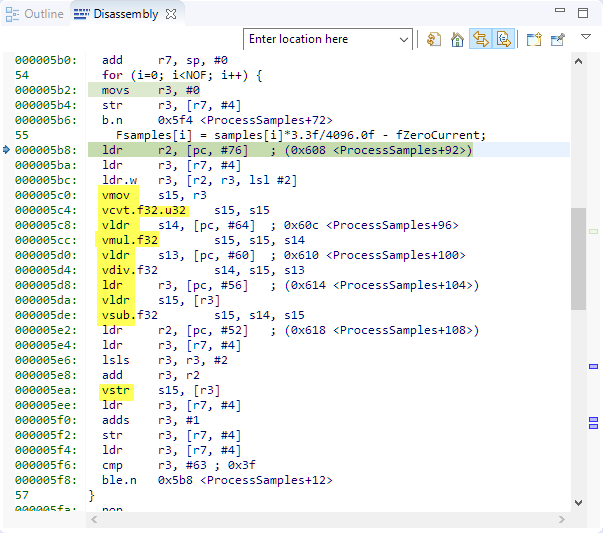

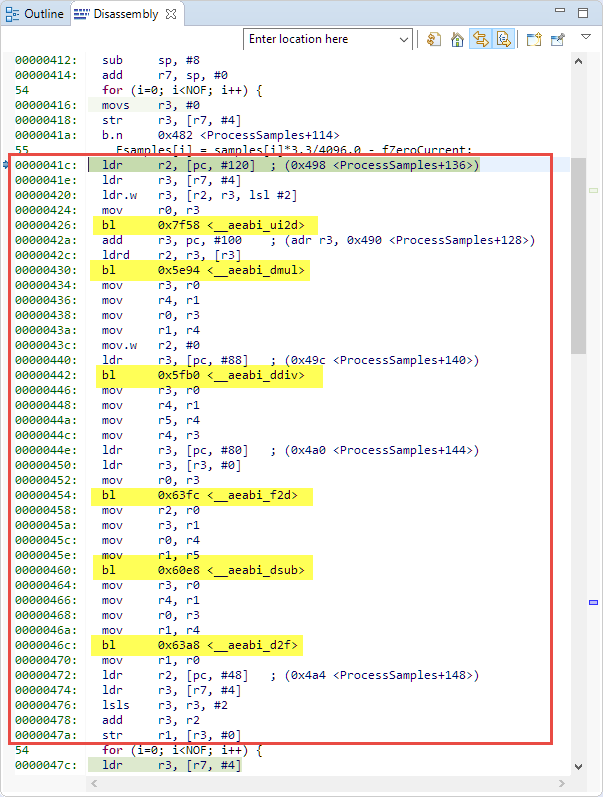

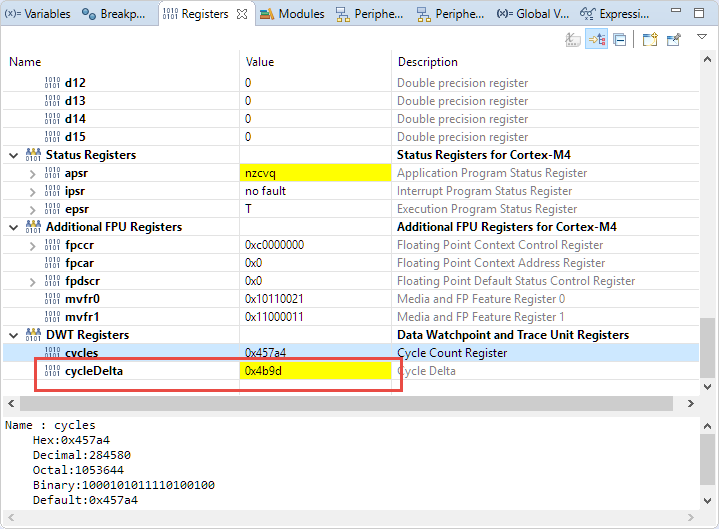

I would like to count the number of Instructions per Cycle executed on an ARM cortexM4 (or cortexM3) processor What it's needed is number of instructions (executed at runtime) of the code I want to profile and number of cycles that the code takes to execute 1 Number of Cycles Use the cycle counter is quite easy and straightforwardMar 29, 19 · The answer is that the ARM CortexM4F has only a *single precision* (float) FPU, and not a double precision (double) FPU As such it only can do float operations in hardware but not for double type The solution in this case is to use float (and not double) constants In C the 'f' suffix can be used to mark constants as floatFor example, the CortexM4F implements the DSP extension as well as the FPv4SP floating point extension In fact, I believe even NEON can be encoded in Thumb2

Tm4c1294kcpdtt3 Texas Instruments Texas Instruments 32bit Arm Cortex M4f Microcontroller Arm9 1mhz 512 Kb Flash 128 Pin Tqfp 914 3068 Rs Components

Which Arm Cortex Cpu Is Right For Your Next Mcu Based Application Digikey

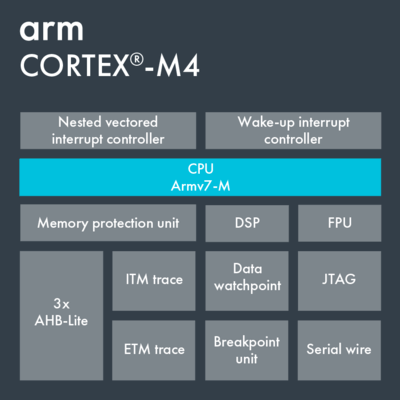

Instruction and Data Cache Controller with 2 Kbytes Cache Memory;ARM CortexM3/M4 Instruction Set & Architecture Universität Dortmund Cortex M4 block diagram 2 Cortex M4 Embedded processor for DSP with FPU Universität Dortmund Cortex M4 vs M3 (b) The CortexM4 ISA is enhanced efficient DSP features including extended singlecycle cycle 16/32bit multiplyView ENGR478_Video 31 lecture3 ARM CortexM4 Assembly Languagepdf from ENG 478 at Central Piedmont Community College ENGR 478 ENGR 478 Design with Microprocessors Lecture 3 Introduction to

Migrating From Cortex M3 To Cortex M4

Arm Introduces Cortex M4 Core For Digital Signal Controllers Berkeley Design Technology Inc

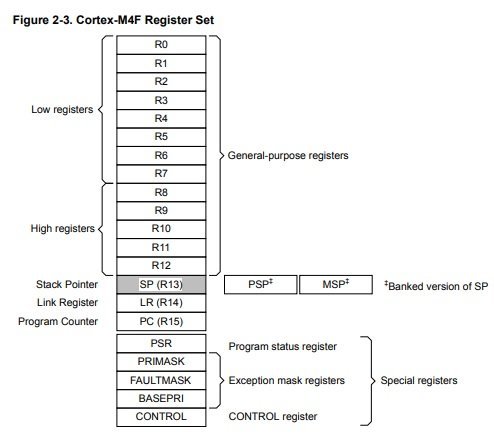

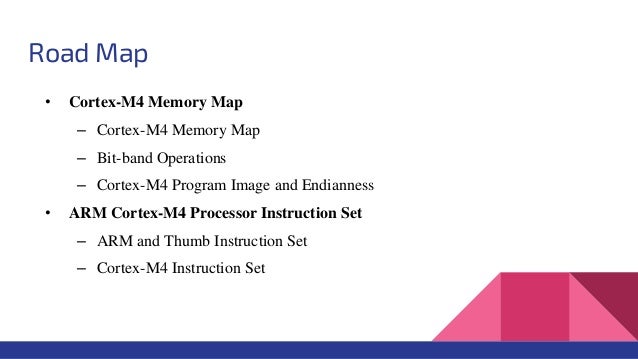

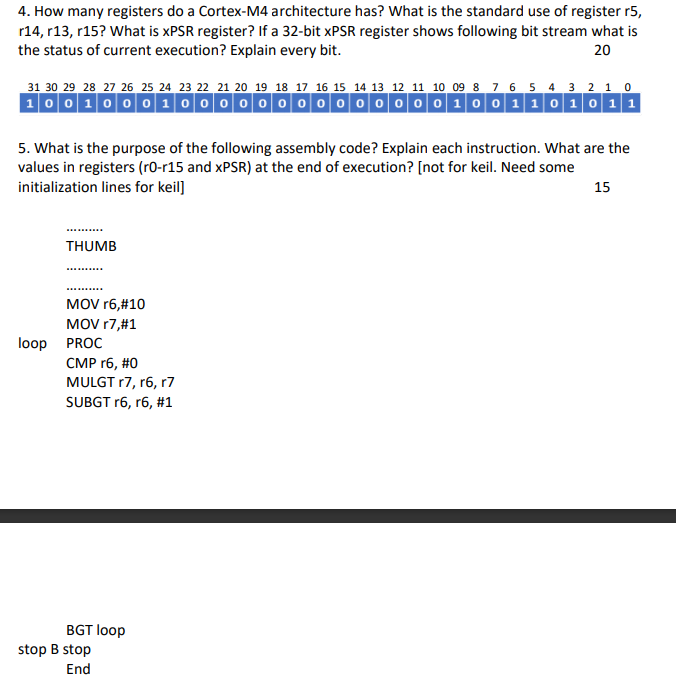

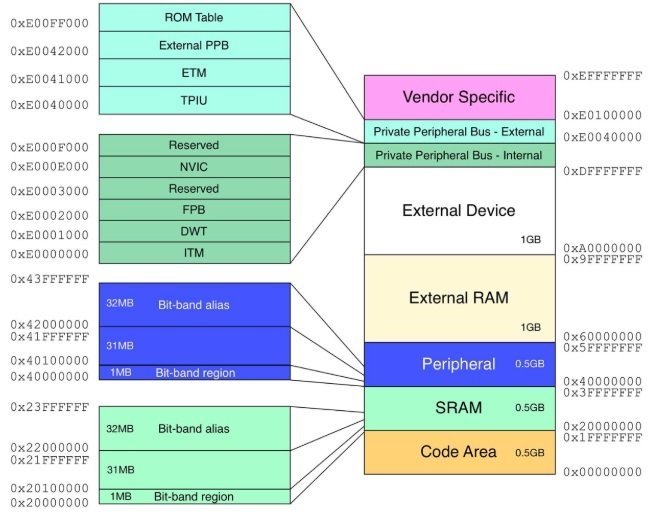

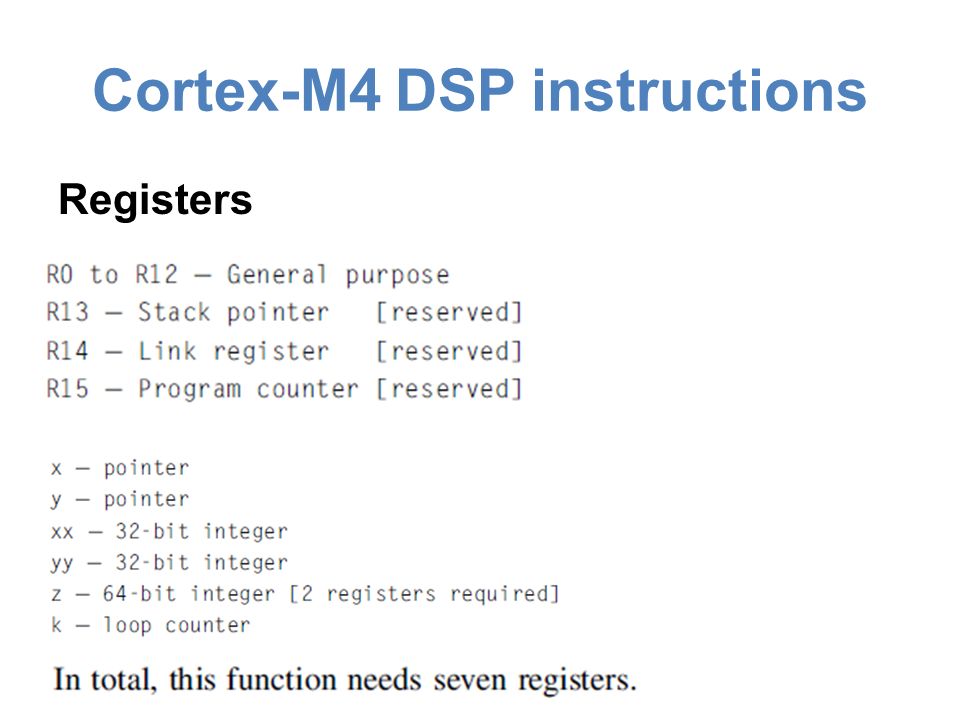

On this site, riscvinstructionsetcom, 'Simulating the RISCV Instruction Set', and 'Using the Imperas OVP Fast Processor Model Simulator with the RISCV Instruction Set', you will see the scope and variety of the RISCV Fast CPU Models available and how easy they are to download and use in C or C simulations 3MPx4 CortexAug 08, 16 · Arm cortexm4 programmer model 1 ARM Zero To Hero Level IBy Mohammed Gomaa 2 ARM programming Model ARM CortexM4F 3 Road Map • CortexM4 Memory Map – CortexM4 Memory Map – Bitband Operations – CortexM4 Program Image and Endianness • ARM CortexM4 Processor Instruction Set – ARM and Thumb Instruction Set – CortexM4̶ ARM CortexM4F running at up to 1 MHz(1) ̶ IEEE® 754 Compliant, Singleprecision FloatingPoint Unit (FPU) ̶ DSP Instruction ̶ Thumb2 instruction set ̶ Instruction and Data Cache Controller with 2 Kbytes of Cache Memory ̶ Memories Up to 32 Kbytes of Embedded SRAM (SRAM1) for Program Code (ICode bus) and Program Data

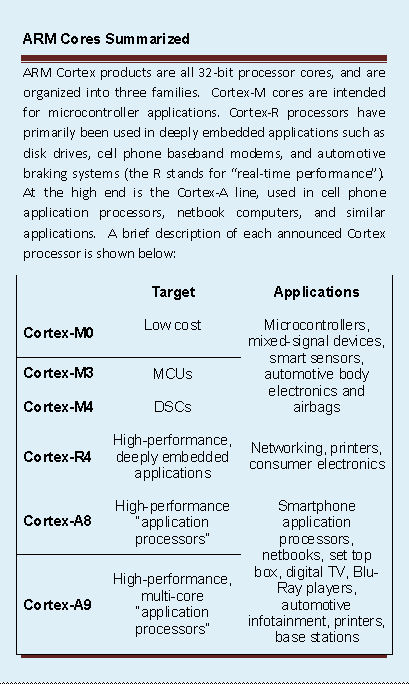

Stm32f415rgt6 Stmicroelectronics Stmicroelectronics Stm32f415rgt6 32bit Arm Cortex M4f Microcontroller Stm32f 168mhz 1 024 Mb Flash 64 Pin Lqfp 746 39p Rs Components

Cortex M4 Fpu And Dsp Instruction Usage In The Stm32f4 Family Youtube

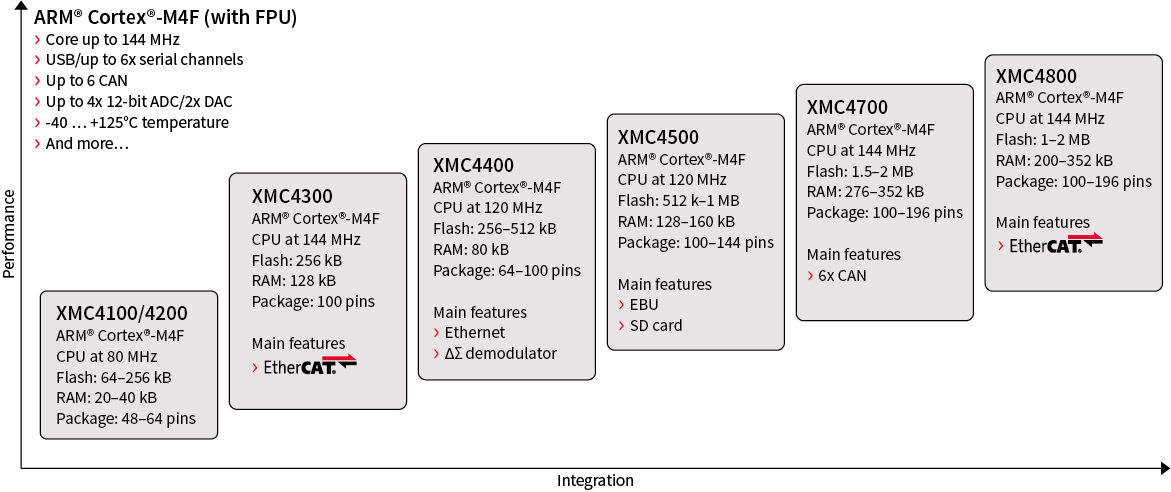

All XMC4000 devices are powered by Arm® Cortex®M4 with a builtin DSP instruction set The Single Precision Floating Point Unit, Direct Memory Access (DMA) feature and Memory Protection Unit (MPU) are stateoftheart for all devices – even the smallest XMC4000 runs with up to 80MHz in core and peripheralsARM®based 32bit Cortex®M4F MCUFPU with 256 to 1024 KB Flash, USB, CAN, 18 timers, 3 ADCs,16 communication interfaces Feature Core ARM® 32bit Cortex®M4F CPU with FPU − 0 MHz maximum frequency, with a memory protection unit (MPU) − Singlecycle multiplication and hardware division − Floating point unit (FPU) − DSP instructionsSo with this particular CortexM4F flavor that was chosen by the MSP432 the device also includes a nested vector interrupt controller for short NVIC It also includes an FPU, Floating Point Unit as well as the enhanced DSP instruction set that comes with the CortexM4

Arm Cortex M4 Microcontrollers Stmicroelectronics

What Is The Top Level Difference In Features Between Cortex M33 And Cortex M4 Trustzone For Armv8 M Forum Trustzone For Armv8 M Arm Community

Apr 21, 21 · Instruction Set Simulator (ISS) for ARM CortexM4F An ISS is a software development tool that takes in instructions for a target processor and executes them The heart of an ISS is the model of the processor Imperas has developed a range of ISS products for use in embedded software development that utilize this fast Fast Processor ModelThis book is for the CortexM4 processor Product revision status The r n p n identifier indicates the revisi on status of the product described in this manual, where351 Syntax64 352 Operation64

The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors Sciencedirect

Stm32f3xxx And Stm32f4xxx Cortex M4 Programming Manual

In addition, the instruction set itself has been vastly expanded;There is an Instruction Set Summary section in the CortexM4F Processor chapter in the data sheet where you can find a list of the supported instructions For more detailed information on the instructions, you can refer to the ARM CortexM4 Technical Reference Manual that can be found on the ARM website hereCortexR and cortexM series is targeted for different requirements and for different applications It is important to know the parameters and features that separates them as there could be applications where both of them can fit in This paper is targeted for such a scenario and helps the Designers for selection The final objective is to help the Designers or Developers to have

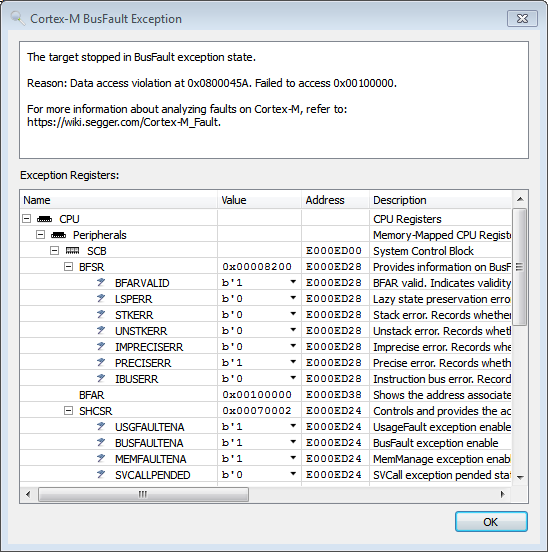

Cortex M Fault Segger Wiki

Arm Cortex M4 Specifics

So the price for choosing CortexM3 over M0, is about 445 times in terms of Area ARM CortexM4 ARM CortexM4 packs even more processing power as compared to M3 It adds 'SMID' (single instruction multiple data) instructions, and completes some instructions in single clock cycle as compared to multi clock cycle execution in M3Mar 13, 15 · To elaborate on the Cortex M4F ARM instruction sets, you'll see that Cortex M4F includes the full ARM instruction set compared to M4 or M3 or M0 This allows you to perform your operations more efficiently You'll also see that a Cortex M4F can process fixed point operations twice as fast as an M3 and over 10 times faster for floating pointARM Cortex M1 – 32bit processor integrated in FPGAs (ARMv6M

32 Bit Xmc4000 Industrial Microcontroller Arm Cortex M4 Infineon Technologies

Be Aware Floating Point Operations On Arm Cortex M4f Mcu On Eclipse

ARM CortexM4 Technical Reference Manual (TRM) This manual contains documentation for the CortexM4 processor, the programmer's model, instruction set, registers, memory map,floating point, multimedia, trace and debug support Product revision statusDescription Access to dedicated SIMD instructions Single Instruction Multiple Data (SIMD) extensions are provided only for CortexM4 and CortexM7 cores to simplify development of application software SIMD extensions increase the processing capability without materially increasing the power consumptionSTM32 Cortex®M4 MCUs and MPUs programming manual Introduction This programming manual provides information for application and systemlevel software developers It gives a full description of the STM32 Cortex®M4 processor programming model, instruction set and core peripherals The applicable products are listed in the table below

Arm Cortex M4 Architecture Microcontrollers Programming

4 How Many Registers Do A Cortex M4 Architecture Chegg Com

A The VMOV instruction (which exists on the CortexM4 already) allows data value to be transferred between general registers and floating point registers According to the Wikipedia, the CortexM7 supports the same instruction set as CortexM4FThe S32K11x contains a CortexM0 with a Von Neumann architecture and the S32K142 contains a CortexM4F with a Harvard architecture as all the S32K14x chips The CortexM0 implements a binary compatible subset of the instruction set and features provided by the CortexM4FMemory Protection Unit (MPU) DSP Instruction;

Question About The Pipeline Clock Cycle And Machine Cycle In Cortex M Series Cortex M M Profile Forum Processors Arm Community

Be Aware Floating Point Operations On Arm Cortex M4f Mcu On Eclipse

01 Arm Cortex M Instruction Set Architecture Youtube

Xmc4400f100k512baxqma1 Infineon Infineon Xmc4400f100k512baxqma1 32bit Cortex M4 Microcontroller Xmc4000 1mhz 512 Kb Flash 100 Pin Lqfp 124 1099p Rs Components

Cortexfamily

Designing With Arm Cortex M4 And A Real Dev Board Ppt Download

Arm Cortex M Wikipedia

Msp432 Mcus And Arm Cortex M4f Core Ti Com Video

Arm Cortex M4 Architecture Microcontrollers Programming

Mixed Signal Dual Core Control Processor With Arm Cortex M4 M0 And 16 Bit Adcs Pdf Free Download

Typecasting In C Under The Hood With Arm Cortex M4 Assembly The Unterminated String

Cortex M4 M7 Simd Instructions Dsp Extension Issue 1 Sfleischman105 Cichlid Github

Arm Cortex M4 Programmer Model

Arm Cortex M0 Instructions Developer Help

4 How Many Registers Do A Cortex M4 Architecture Chegg Com

Arm Cortex M4 Architecture Microcontrollers Programming

Arm Cortex M4 Microcontrollers Stmicroelectronics

How To Decode Armv7 Instructions Electrical Engineering Stack Exchange

Arm Architecture Wikiwand

Migrating From Cortex M3 To Cortex M4

Arm Cortex M4 Programmer Model

Cortex M4 Technical Reference Manual

Arm Programming Tutorial 15 Branch Instruction Set In Arm Part 1 Youtube

Catching The String Thoughts On Arm Cortex M Differences

Noisefloor Boundary Conditions And Peripheral Interfaces

Technical Reference Manual Arm Information Center Technical Reference Manual Arm Information Center Pdf Pdf4pro

Datasheet Review High Performance Stm32 Cortex M4 Microcontroller

Arm Cortex M3 And Cortex M4 Processors Ppt Download

Arm Cortex M4 Programmer Model

Arm Cortex M7 Digital Signal Processing Drives Family Evolution Berkeley Design Technology Inc

Cortex M4f Lazy Fpu Stacking Stack Overflow

Be Aware Floating Point Operations On Arm Cortex M4f Mcu On Eclipse

Cortex M4f Instruction Set Simulators Iss For Simulating Risc V Cores

Ti S 32 Bit Successor To The 16 Bit Mcu Ee Times

Arm Cortex M4 Microcontrollers Stmicroelectronics

Arm Cortex M Wikiwand

Stm32 Wikipedia

Catching The String Thoughts On Arm Cortex M Differences

Arm Cortex M4 F System Design

Arm Cortex M4 M7 Advanced Tips 2 Simd Instructions Youtube

Catching The String Thoughts On Arm Cortex M Differences

Arm Cortex M

Stm32f405rgt6 Stmicroelectronics Stmicroelectronics 32bit Arm Cortex M4f Microcontroller Stm32f 168mhz 1 024 Mb Flash 64 Pin Lqfp 9 6456 Rs Components

3 2 17 Richard Kuo Assistant Professor Ppt Video Online Download

Noisefloor Boundary Conditions And Peripheral Interfaces

4 How Many Registers Do A Cortex M4 Architecture Chegg Com

Investigating Arm Cortex M33 Core With Trustzone Dsp Acceleration 1 Mcu On Eclipse

Cortex M Processors And The Internet Of Things Iot

Arm Cortex M4 Programmer Model

Click To Edit Master Title Style Basics Of Embedded Systems Iax0230 Arm Cortex M Architecture Prof Dr Kalle Tammemae Prof Dr Ing Thomas Hollstein Ppt Download

Arm Cortex M0 Instructions Developer Help

Tm4c1299nczadi3 Texas Instruments Texas Instruments Tm4c1299nczadi3 32bit Arm Cortex M4f Microcontroller Arm9 1mhz 1 024 Mb Flash 212 Pin Nfbga 914 3070 Rs Components

Basics Of Embedded Systems Iax0230 Arm Cortex M Architecture Ppt Download

The Cortex M3 M4 Embedded Systems Cortex M3 M4 Instruction Sets Ppt Download

Arm Cortex M Wikiwand

Air Supply Lab Lesson 02 Arm Cortex M Instruction Set

Which Arm Cortex Cpu Is Right For Your Next Mcu Based Application Digikey

Air Supply Lab Lesson 02 Arm Cortex M Instruction Set

Designing With Arm Cortex M4 And A Real Dev Board Ppt Download

Be Aware Floating Point Operations On Arm Cortex M4f Mcu On Eclipse

0 件のコメント:

コメントを投稿